——Faasoa mai le DWIN Froum

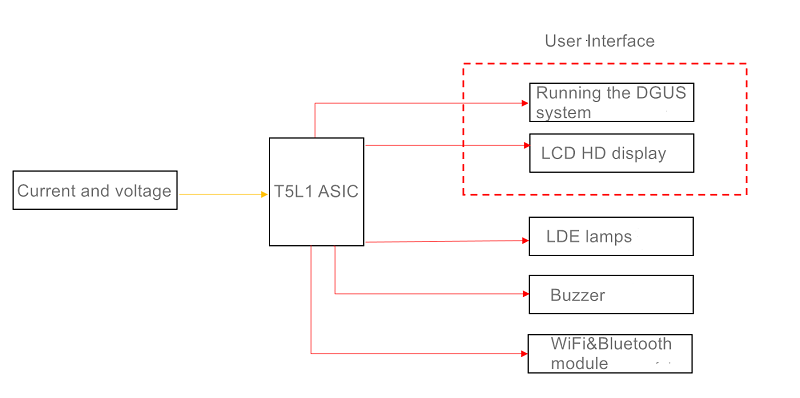

Faʻaaogaina le DWIN T5L1 puʻe e avea ma faʻatonuga o le masini atoa, mauaina ma faʻagasolo le paʻi, mauaina o le ADC, faʻamatalaga faʻatonutonu PWM, ma faʻaulu le 3.5-inisi LCD mata e faʻaalia ai le tulaga o loʻo iai i le taimi moni.Lagolago le fetuutuunaiga mamao pa'i ole malamalama puna malamalama LED e ala i le WiFi module, ma lagolago leo leo.

Vaega o polokalame:

1. Faʻaaogaina le pulou T5L e tamoe i le tele o taimi, AD analog sampling e mautu, ma o le mea sese e laʻititi;

2. Lagolago TYPE C fesoʻotaʻi saʻo ile PC mo le faʻapipiʻiina ma le susunuina o polokalame;

3. Lagolago maualuga-saosaoa OS autu autu, 16bit taulaga tutusa;UI autu PWM uafu, AD uafu taʻitaʻia i fafo, taugofie tau talosaga mamanu, leai se manaʻoga e faʻaopoopo MCU faaopoopo;

4. Lagolago WiFi, Bluetooth mamao mamao;

5. Lagolago 5 ~ 12V DC lautele voltage ma lautele faʻaoga faʻaoga

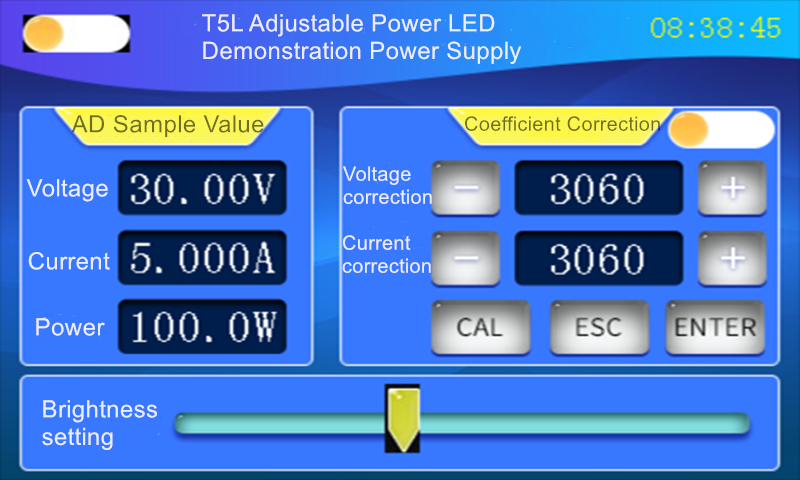

1.1 Fuafuaga ata

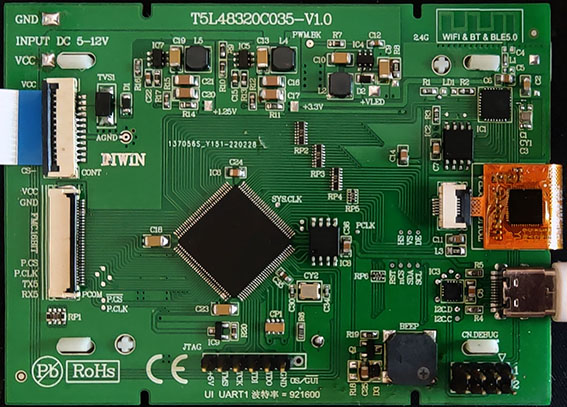

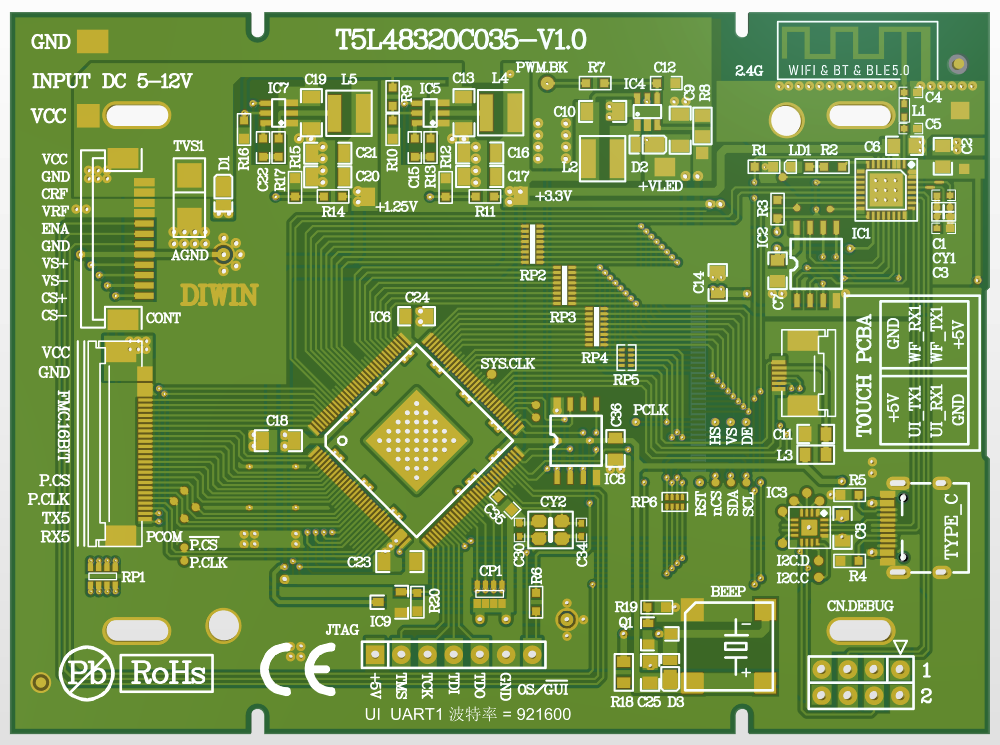

1.2 laupapa PCB

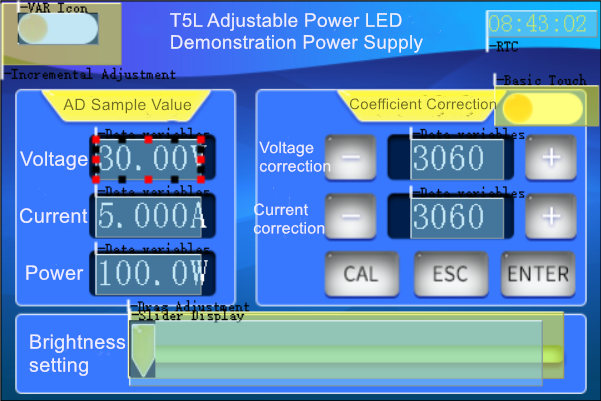

1.3 Fa'aoga fa'aoga

Folasaga maasiasi:

(1) Fa'asologa o masini komepiuta

1.4 T5L48320C035 fa'asologa fa'asologa

1. MCU logic power supply 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. MCU autu mana tu'uina atu 1.25V: C23, C24;

3. MCU analog mana tu'uina atu 3.3V: C35 o le sapalai mana analog mo MCU.Pe a faʻapipiʻi, e mafai ona tuʻufaʻatasia le eleele autu 1.25V ma le eleele faʻatatau, ae tatau ona vavae ese le eleele analog.O le eleele analog ma le eleele numera e tatau ona aoina i le pou le lelei o le LDO output capacitor tele, ma e tatau foi ona aoina le pou lelei analog i le pou lelei o le LDO capacitor tele, ina ia faaitiitia AD sampling Pisa.

4. AD analog signal acquisition circuit: CP1 o le AD analog input filter capacitor.Ina ia faʻaitiitia le faʻataʻitaʻiga mea sese, o le analog ground ma numera numera o le MCU e tuʻueseese tutoatasi.O le pou le lelei o le CP1 e tatau ona faʻafesoʻotaʻi i le eleele analog o le MCU ma le faʻaitiitia o le faʻalavelave, ma o le lua tutusa capacitors o le oscillator tioata e fesoʻotaʻi i le eleele analog o le MCU.

5. Fa'aili fa'aili: C25 o le fa'aogaina o le eletise mo le fa'amalo.O le faʻamalo o se masini faʻaogaina, ma o le ai ai se maualuga maualuga i le taimi o le gaioiga.Ina ia faʻaitiitia le tumutumu, e manaʻomia le faʻaitiitia o le MOS o loʻo i ai nei o le buzzer e faʻaogaina ai le paipa MOS i le laina laina, ma mamanuina le matagaluega e faʻaogaina i le suiga.Manatua e tatau ona fa'afeso'ota'i tutusa le R18 i pito uma e lua o le fa'amalo e fetu'una'i ai le lelei o le leo o le fa'amalo ma fa'amalie le leo ma le manaia.

6. WiFi ta'amilosaga: WiFi chip sampling ESP32-C, ma WiFi + Bluetooth + BLE.I luga o le uaea, o le eleele eletise RF ma le faʻailoga faʻailoga e vavae ese.

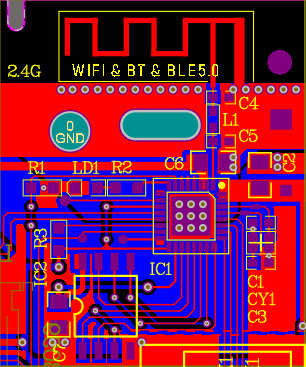

1.5 fa'asologa o le WiFi

I le ata o loʻo i luga, o le pito i luga o le paʻu apamemea o le faʻaogaina o le eleele eletise.E tatau ona i ai se vaega tele i le eleele o le eletise o le WiFi antenna, ma o le nofoaga e aoina ai le eletise o le pou leaga o le C6.E manaʻomia ona tuʻuina atu se faʻaaliga faʻaalia i le va o le eletise ma le WiFi antenna, o lea e tatau ai ona i ai se paʻu apamemea i lalo ole antenna WiFi.O le umi o le paʻu apamemea e sili atu i le umi faʻaopoopoga o le antenna WiFi, ma o le faʻaopoopoga o le a faʻateleina ai le lagona o le WiFi;fa'asino ile pou leaga ole C2.O se vaega tele o le kopa e mafai ona puipuia le pisapisao e mafua mai i le WiFi antenna radiation.O eleele apamemea e 2 e tuueseese i le pito i lalo ma aoina i le ogatotonu o le ESP32-C e ala i vias.E manaʻomia e le eletise eletise RF se faʻalavelave maualalo nai lo le faʻamaufaʻailoga o le eleele, o lea e iai 6 vias mai le eletise eletise i le pulou puʻe e faʻamautinoa ai le maualalo o le faʻalavelave.O le matasele eleele o le oscillator tioata e le mafai ona maua le mana RF e tafe ai, a le o le oscillator tioata o le a faʻatupuina le faʻavevesi, ma o le a le mafai e le WiFi faʻavevesi ona lafo ma maua faʻamatalaga.

7. Backlight LED eletise sapalai matagaluega: SOT23-6LED avetaavale chip sampling.O le DC/DC power supply i le LED e fai tuto'atasi se matasele, ma le DC/DC ground e feso'ota'i ile 3.3V LOD ground.Talu ai o le PWM2 port core ua faʻapitoa, e faʻaalia ai le 600K PWM faʻailoga, ma faʻaopoopoina le RC e faʻaoga ai le PWM o se faʻatonuga ON / OFF.

8. Voltage input range: lua DC/DC step-down ua mamanuina.Manatua o le R13 ma le R17 tetee i le DC / DC e le mafai ona faʻaumatia.O tupe meataalo DC / DC e lua e lagolagoina i le 18V faʻaoga, lea e faigofie mo le tuʻuina atu o le eletise i fafo.

9. USB TYPE C uafu debug: Ituaiga C e mafai ona fa'apipi'i ma tatala i luma ma tua.O le faʻaofiina i luma e fesoʻotaʻi ma le WIFI chip ESP32-C e faʻapipiʻi le WIFI chip;fa'aofi fa'afeagai feso'ota'i ma le XR21V1410IL16 e fa'apolokalame le T5L.TYPE C lagolago 5V power supply.

10. Feso'ota'iga uafu tutusa: T5L OS autu o lo'o i ai le tele o ports IO e leai se totogi, ma e mafai ona mamanuina feso'ota'iga tu'usa'o 16bit.Faʻatasi ma le ST ARM FMC parallel port protocol, e lagolagoina le faitau ma le tusitusi faʻatasi.

11. LCM RGB maualuga-saoasaoa atinaʻe mamanu: T5L RGB gaioiga e fesoʻotaʻi saʻo i le LCM RGB, ma faʻapipiʻi le paʻu i le ogatotonu e faʻaitiitia ai le faʻalavelave vai o le LCM.Pe a fai uaea, faʻaitiitia le umi o le fesoʻotaʻiga faʻafesoʻotaʻi RGB, aemaise lava le faailo PCLK, ma faʻateleina le faʻaogaina o le RGB PCLK, HS, VS, DE suʻega suʻega;o le SPI uafu o le lau e fesoʻotaʻi atu i le P2.4 ~ P2.7 ports o le T5L, lea e faigofie mo le mamanuina o le avetaavale lau.Ta'ita'i ese vaega ole su'ega RST, nCS, SDA, SCI e fa'afaigofie ai le atina'eina o le polokalama fa'avae.

(2) fa'aoga DGUS

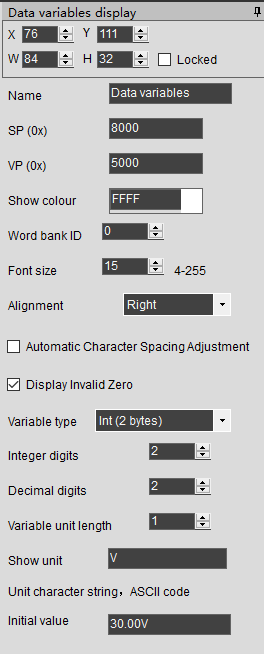

1.6 Fa'atonuga fa'aaliga fesuia'i fa'amaumauga

(3) OS

//——————————— DGUS faitau ma tusitusi faatulagaga

typedef struct

{

u16 faaopoopo;//UI 16bit tuatusi fesuiai

u8 datLen;//8bitdata umi

u8 *pBuf;// 8bit faʻamatalaga faʻamatalaga

} UI_packTypeDef;//DGUS faitau ma tusi pepa

//——————————-faʻatonu faʻaaliga faʻaalia faʻamatalaga

typedef struct

{

u16 VP;

u16 X;

u16 Y;

u16 Lanu;

u8 Lip_ID;

u8 Fuafuaga Tele;

u8 Fa'aopoopo;

u8 IntNum;

u8 TesNumera;

u8 Ituaiga;

u8 LenUint;

u8 StringUinit[11];

} Numera_spTypeDef;//fa'asologa fa'amatalaga fesuia'i fa'amatalaga

typedef struct

{

Numera_spTypeDef sp;//fa'amatala SP fa'amatalaga fa'asino

UI_packTypeDef spPack;//fa'amatala SP variable DGUS faitau ma tusi afifi

UI_packTypeDef vpPack;//fa'amatala vp fesuia'i DGUS faitau ma tusi afifi

} Numera_HandleTypeDef;//fa'amatalaga fesuia'i fausaga

Fa'atasi ai ma le fa'amatalaga o le au fa'amatalaga muamua.Le isi, fa'amatala se fesuiaiga mo le fa'aaliga sampling voltage:

Numera_HandleTypeDef Hsample;

u16 voltage_sample;

Muamua, faʻatino le galuega amata

NumeraSP_Init(&Hsample,voltage_sample,0×8000);//0 × 8000 o le faʻamatalaga faʻamatalaga

//——Fesuiaiga o faʻamaumauga o loʻo faʻaalia ai le faʻavaeina o le fausaga o le SP——

fa'aleaogaina NumeraSP_Init(Number_HandleTypeDef *numera,u8 *taua, u16 numeraAddr)

{

numera->spPack.addr = numeraAddr;

numera->spPack.datLen = sizeof(numera->sp);

numera->spPack.pBuf = (u8 *)&numera->sp;

Faitau_Dgus(&numera->spPack);

numera->vpPack.addr = numera->sp.VP;

sui (numera->sp.Type) //O le umi o faʻamatalaga o le vp fesuiaʻi e otometi lava ona filifilia e tusa ai ma le faʻasologa o faʻamatalaga faʻasologa ua fuafuaina i le DGUS interface.

{

mataupu 0:

mataupu 5:

numera->vpPack.datLen = 2;

malepe;

mataupu 1:

mataupu 2:

mataupu 3:

mataupu 6:

numera->vpPack.datLen = 4;

mataupu 4:

numera->vpPack.datLen = 8;

malepe;

}

numera->vpPack.pBuf = tau;

}

A maeʻa le amataina, Hsample.sp o le faʻamatalaga faʻamatalaga o le fesuiaiga o faʻamatalaga faʻataʻitaʻiga voltage;Hsample.spPack o le faʻamatalaga fesoʻotaʻiga i le va o le OS core ma le UI voltage sampling data variable e ala i le DGUS interface function;Hsample.vpPack o le uiga o le suia o le voltage sampling data variable, e pei o le font Colors, ma isi mea faapena e pasi atu foi i le UI autu e ala i le DGUS interface function.Hsample.vpPack.addr o le voltage sampling data variable address, lea na otometi lava ona maua mai le galuega amata.A e suia le tuatusi fesuiaiga poʻo le fesuiaiga o faʻamatalaga faʻamatalaga i le DGUS interface, e leai se manaʻoga e faʻafouina le tuatusi fesuiaʻi i le OS core synchronously.A maeʻa ona faʻatusatusa e le OS autu le fesuiaiga o voltage_sample, e naʻo le manaʻomia o le faʻatinoina o le Write_Dgus (&Hsample.vpPack) galuega e faʻafouina ai.E leai se manaʻoga e faʻapipiʻi le voltage_sample mo le faʻasalalauga DGUS.

Taimi meli: Iuni-15-2022